PRELIMINARY November 2009

# **AR7241: A High Performance And Cost-Effective Network Processor**

## **General Description**

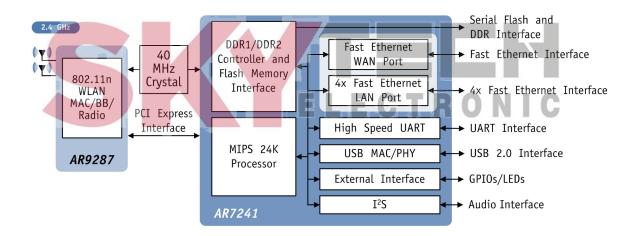

The Atheros AR7241 is a high performance and cost effective network processor for access point, router, and gateway applications. It includes a MIPS 24K processor, PCI Express host interface, integrated 802.3 Ethernet Switch with five 10/100 Mbps Fast Ethernet MAC/PHY, one USB 2.0 MAC/PHY, and external memory interface for serial Flash, DDR1 or DDR2 interface, an I<sup>2</sup>S audio interface, a high-speed UART, and GPIOs that can be used for LED controls or other general purpose interface configurations.

The AR7241 is a memory-centric architecture including various DMA controlled interfaces that access the DDR memory.

The AR7241 network processor, when paired with the AR9287 single chip 802.11n MAC/BB/Radio family, provides the best-in-class WLAN solution capable of supporting 802.11b/g/n standards.

## **Features**

- Integrated MIPS 24 K 32-bit processor operating at up to 400 MHz

- 64 K instruction cache and 32 K data cache

- Integrated Ethernet Switch with four 10/ 100 802.3 Ethernet LAN ports and one WAN port

- 16-bit DDR1 or DDR2 memory interface supporting up to 400 M transfers per second

- An external serial Flash memory interface (maximum 16 MBytes)

- One USB 2.0 controller with built-in MAC/ PHY support

- High-speed UART and multiple GPIO pins for general purpose I/O or LED control

- A single lane PCI Express 1.1 interface that can be used for interfacing to the AR9287 single chip 802.11n MAC/BB/Radio

- JTAG port support for processor core

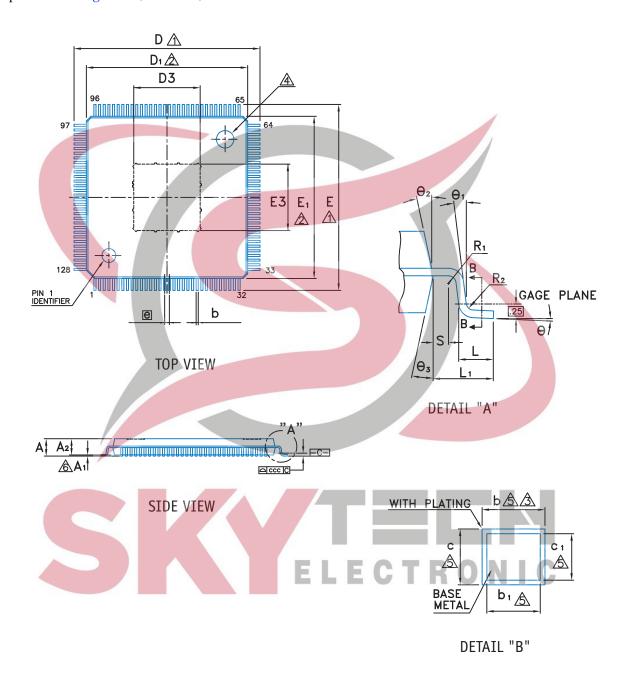

- 14 mm x 14 mm 128-pin LQFP lead-free package

## System Block Diagram

COMPANY CONFIDENTIAL • 1

<sup>© 2009</sup> by Atheros Communications, Inc. All rights reserved. Atheros®, Atheros Driven®, Atheros XR®, Driving the Wireless Future®, ROCm®, Super A/G®, Super G®, Super N®, Total 802.11®, XSPAN®, Wireless Future. Unleashed Now.®, and Wake on Wireless® are registered by Atheros Communications, Inc. Atheros SST™, Signal-Sustain Technology™, the Air is Cleaner at 5-GHz™, and 5-UP™ are trademarks of Atheros Communications, Inc. The Atheros logo is a registered trademark of Atheros Communications, Inc. All other trademarks are the property of their respective holders. Subject to change without notice.

## **Table of Contents**

| General Description                   |     |

|---------------------------------------|-----|

| Features                              |     |

| System Block Diagram                  | 1   |

| 1 Pin Descriptions                    | 5   |

| 2 System Architecture                 | 15  |

| 2.1 MIPS Processor                    |     |

| 2.2 Configuration                     |     |

| 2.3 AR7241 Address MAP                | 17  |

| 2.4 AHB Master Bus                    |     |

| 2.5 APB Bridge                        | 17  |

| 2.6 DDR Memory Controller             | 17  |

| 2.7 Serial Flash (SPI)                | 18  |

| 2.8 UART                              | 18  |

| 2.9 GE0 and GE1                       | 19  |

| 2.10 MDC/MDIO Interface               |     |

| 2.11 Ethernet Switch Controller       | 20  |

| 2.11.1 VLANs For LAN Ports            | 22  |

| 2.11.2 Quality of Service (QoS) For I | LAN |

| Ports                                 | 23  |

| 2.12 Rate Limiting                    | 23  |

| 2.13 Broadcast Storm Control          | 24  |

| 2.14 Switch Operation                 | 24  |

| 2.15 Port Mirroring                   | 24  |

| 2.16 Port States                      |     |

| 3 Audio Interface                     | 25  |

| 3.1 Overview                          | 25  |

| 3.2 Audio PLL                         |     |

| 3.3 I <sup>2</sup> S Interface        |     |

| 3.3.1 External DAC                    | 1// |

| 3.3.2 Sample Sizes and Rates          |     |

| 3.3.3 Stereo Software Interface       |     |

| 3.4 SPDIF INTERFACE                   | 26  |

| 3.5 MAILBOX (DMA CONTROLLER)          | 27  |

| 3.5.1 Mailboxes                       |     |

| 3.5.2 MBOX DMA Operation              |     |

| 3.5.3 Software Flow Control           |     |

| 3.5.4 Mailbox Error Conditions        | 28  |

| 3.5.5 MBOX-Specific Interrupts        | 28  |

| = *                                   |     |

| 4.1 | Absolute Maximum Ratings2                 | 9 |

|-----|-------------------------------------------|---|

| 4.2 | Recommended Operating Conditions 2        | 9 |

| 4.3 | General DC Electrical Characteristics . 3 | 0 |

| 4.4 | 40 MHz Clock Characteristics 3            | 2 |

| 4.5 | Power Consumption3                        | 3 |

| 5   | Package Dimensions3                       | 5 |

| 6   | Ordering Information3                     | 7 |

4 Electrical Characteristics ........... 29

## 1. Pin Descriptions

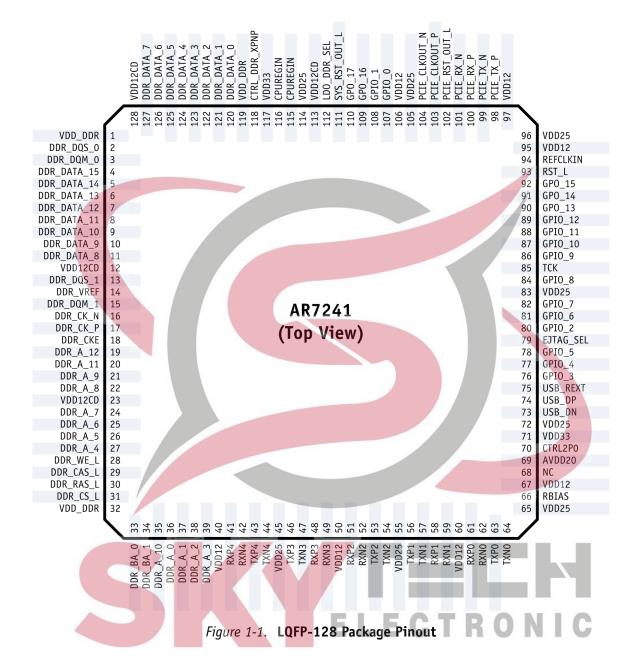

This section contains a package pinout (see Figure 1-1 and Table 1-2) and a tabular listing of the signal descriptions.

This nomenclature is used for signal names:

| NC | No connection should be made to |

|----|---------------------------------|

|    | this pin                        |

- $_{L}$ At the end of the signal name, indicates active low signals

- P At the end of the signal name, indicates the positive side of a differential signal

- At the end of the signal name N indicates the negative side of a differential signal

This nomenclature is used for signal types:

- Ι Digital input signal

- I/O A digital bidirectional signal

- IΑ Analog input signal

- IA/OA Analog bidirectional signal

- ΙH Input signals with weak internal pull-up, to prevent signals from floating when left open

- IL Input signals with weak internal pull-down, to prevent signals from floating when left open

- O A digital output signal

- OA An analog output signal

- OD A digital output signal with open drain

- Р A power or ground signal

Figure 1-1 shows the LQFP-128 AR7241 pinout.

Table 1-1 shows the multiplexed pins for the AR7241,

Table 1-1. Multiplexed Pins<sup>[1][2]</sup>

| LQFP-128 |          |                                      |                |                            |                       |                       |

|----------|----------|--------------------------------------|----------------|----------------------------|-----------------------|-----------------------|

| Pin      | GPIO Pin | EJTAG Pin                            | LED Pin        | SPDIF/I <sup>2</sup> S Pin | SPI Pin               | UART Pin              |

| 107      | GPIO_0   |                                      |                | I2S_WS (FN2, 4)            | SPI_CS_1<br>(FN1, 14) |                       |

| 108      | GPIO_1   |                                      |                | I2S_CK (FN2, 3)            | SPI_CS_2<br>(FN1, 13) |                       |

| 80       | GPIO_2   |                                      |                |                            | SPI_CS_0<br>(FN1, 18) |                       |

| 76       | GPIO_3   |                                      |                |                            | SPI_CLK<br>(FN1, 18)  |                       |

| 77       | GPIO_4   |                                      |                |                            | SPI_MOSI<br>(FN1, 18) |                       |

| 78       | GPIO_5   |                                      |                |                            | SPI_MISO<br>(FN1, 18) |                       |

| 81       | GPIO_6   | TDI <sup>[3]</sup> (FN1, 0)          |                | I2S_CK (FN1, 26)           |                       |                       |

| 82       | GPIO_7   | TDO <sup>[3]</sup> (FN1, 0)          |                | I2S_WS (FN1, 26)           |                       |                       |

| 84       | GPIO_8   | TMS <sup>[3]</sup> (FN1, 0)          |                | I2S_SD (FN1, 26)           |                       |                       |

| 86       | GPIO_9   |                                      |                |                            |                       | UART_SIN<br>(FN1, 1)  |

| 87       | GPIO_10  |                                      |                |                            |                       | UART_SOUT<br>(FN1, 1) |

| 88       | GPIO_11  |                                      |                | I2S_MCK<br>(FN1, 26, 27)   |                       | UART_RTS<br>(FN1, 2)  |

|          | GPIO_12  |                                      |                | I2S_MICIN (FN1, 26)        |                       | UART_CTS              |

| 89       |          |                                      |                | I2S_SD (FN2, 5)            |                       | (FN1, 2)              |

| 90       | GPO_13   |                                      | LED_0 (FN1, 3) | SPDIF_OUT<br>(FN1, 30)     |                       | _                     |

| 91       | GPO_14   |                                      | LED_1 (FN1, 4) | I2S_SD (FN2, 1)            |                       |                       |

| 92       | GPO_15   |                                      | LED_2 (FN1, 5) | I2S_WS (FN2, 1)            |                       |                       |

| 109      | GPO_16   |                                      | LED_3 (FN1, 6) | I2S_CK (FN2, 1)            |                       |                       |

| 110      | GPO_17   |                                      | LED_4 (FN1, 7) | ECTR                       | ON                    | C                     |

| 85       | GPIO_18  | TCK <sup>[3]</sup> (FN1, 0)          |                | SPDIF_OUT<br>(FN1, 30, 31) |                       |                       |

| 79       | GPIO_19  | EJTAG_SEL <sup>[3]</sup><br>(FN1, 0) |                |                            |                       |                       |

<sup>[1]</sup> Multiplexing of the GPIO pins is controlled by the registers "GPIO Function (GPIO\_FUNCTION\_1)" on page 50 and "Extended GPIO Function Control (GPIO\_FUNCTION\_2)" on page 51.

<sup>[2]</sup>Notations of (FNx, y) indicate that the pin is controlled by the particular register and bit. For example, (FN1, 30, 31) indicates the "GPIO Function (GPIO\_FUNCTION\_1)" register, bit [30] and bit [31], and (FN2, 1) indicates the "Extended GPIO Function Control (GPIO\_FUNCTION\_2)" register, bit [1].

<sup>[3]</sup> The EJTAG interface is enabled by default. To use the EJTAG interface as GPIO pins, the JTAG\_DISABLE bit in the "GPIO Function (GPIO\_FUNCTION\_1)" register must be set to 1.

Table 1-2. Signal-to-Pin Relationships and Descriptions

|                         | LQFP-128 |       |                                                                                                                                                                                                                                                                               |  |

|-------------------------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol                  | Pin      | Type  | Description                                                                                                                                                                                                                                                                   |  |

| Reset and Clock         |          |       |                                                                                                                                                                                                                                                                               |  |

| REFCLKIN                | 94       | I     | 40 MHz reference clock input, AC coupled, can be sine wave or square wave. An external 100 pF capacitor should connect between REFCLKIN and the clock source. See Table 4-7 and Table 4-8 on page 32 for more information.                                                    |  |

| RST_L                   | 93       | IH    | Power on reset with internal weak pull-up. Refer to reference design schematics                                                                                                                                                                                               |  |

| SYS_RST_OUT_L           | 111      | OD    | System reset out, open drain, pull up is required                                                                                                                                                                                                                             |  |

| PCI Express             |          |       |                                                                                                                                                                                                                                                                               |  |

| PCIE_CLKOUT_N           | 104      | OA    | Differential reference clock (100 MHz)                                                                                                                                                                                                                                        |  |

| PCIE_CLKOUT_P           | 103      | OA    |                                                                                                                                                                                                                                                                               |  |

| PCIE_RST_OUT_L          | 102      | OD    | PCI Express reset, open drain                                                                                                                                                                                                                                                 |  |

| PCIE_RX_N               | 101      | IA    | Differential receive                                                                                                                                                                                                                                                          |  |

| PCIE_RX_P               | 100      | IA    |                                                                                                                                                                                                                                                                               |  |

| PCIE_TX_N               | 99       | OA    | Differential transmit                                                                                                                                                                                                                                                         |  |

| PCIE_TX_P               | 98       | OA    |                                                                                                                                                                                                                                                                               |  |

| Serial Interface        |          |       |                                                                                                                                                                                                                                                                               |  |

| SPI_CLK <sup>[1]</sup>  | 76       | О     | Serial interface clock                                                                                                                                                                                                                                                        |  |

| SPI_CS_0 <sup>[1]</sup> | 80       | 0     | SPI chip select                                                                                                                                                                                                                                                               |  |

| SPI_CS_1 <sup>[1]</sup> | 107      | 0     |                                                                                                                                                                                                                                                                               |  |

| SPI_CS_2 <sup>[1]</sup> | 108      | 0     |                                                                                                                                                                                                                                                                               |  |

| SPI_MOSI <sup>[1]</sup> | 77       | 0     | Data transmission from the AR7241 to an external device. On reset, SPI_MISO (GPIO_5) is input and SPI_MOSI (GPIO_4) is output so it can directly interface with a SPI device such as a serial flash. If a serial flash is not used, these pins may be used as GPIO pins.      |  |

| SPI_MISO <sup>[1]</sup> | 78       | IL    | Data transmission from an external device to the AR7241. On reset, SPI_MISO (GPIO_5) is input and SPI_MOSI (GPIO_4) is output so that it can directly interface with a SPI device such as a serial flash. If a serial flash is not used, these pins may be used as GPIO pins. |  |

| USB                     |          |       |                                                                                                                                                                                                                                                                               |  |

| USB_DM                  | 73       | IA/OA | USB 2.0 D- data pin                                                                                                                                                                                                                                                           |  |

| USB_DP                  | 74       | IA/OA | USB 2.0 D+ data pin                                                                                                                                                                                                                                                           |  |

| USB_REXT                | 75       | IA/OA | Connect to external $6.04~\mathrm{K}\Omega$ resistor                                                                                                                                                                                                                          |  |

| UART                    |          |       |                                                                                                                                                                                                                                                                               |  |

| UART_CTS <sup>[1]</sup> | 89       | I     | UART clear to send signal                                                                                                                                                                                                                                                     |  |

| UART_RTS <sup>[1]</sup> | 88       | О     | UART ready to send signal (optional UART interface pin)                                                                                                                                                                                                                       |  |

| UART_SIN <sup>[1]</sup> | 86       | I     | Serial data in                                                                                                                                                                                                                                                                |  |

*Table 1-2.* Signal-to-Pin Relationships and Descriptions (continued)

|                          | LQFP-128 |      |                                                   |

|--------------------------|----------|------|---------------------------------------------------|

| Symbol                   | Pin      | Type | Description                                       |

| UART_SOUT <sup>[1]</sup> | 87       | О    | Serial data out                                   |

| DDR                      |          |      |                                                   |

| DDR_BA_0                 | 33       | О    | DDR bank address                                  |

| DDR_BA_1                 | 34       | О    |                                                   |

| DDR_CS_L                 | 31       | О    | DDR chip select                                   |

| DDR_CK_N                 | 16       | О    | DDR clock                                         |

| DDR_CK_P                 | 17       | 0    |                                                   |

| DDR_CKE                  | 18       | 0    | DDR clock enable                                  |

| DDR_DQM_0                | 3        | 0    | DDR data mask                                     |

| DDR_DQM_1                | 15       | 0    |                                                   |

| DDR_DQS_0                | 2        | I/O  | DDR data strobe                                   |

| DDR_DQS_1                | 13       | I/O  | In DDR2, both polarity signals need to be driven. |

| DDR_CAS_L                | 29       | 0    | DDR column address strobe                         |

| DDR_RAS_L                | 30       | 0    | DDR row address strobe                            |

| DDR_WE_L                 | 28       | 0    | DDR write enable                                  |

| DDR_VREF                 | 14       | I    | DDR reference level for SSTL signals              |

| DDR_A_0                  | 36       | 0    | DDR address                                       |

| DDR_A_1                  | 37       | 0    |                                                   |

| DDR_A_2                  | 38       | 0    |                                                   |

| DDR_A_3                  | 39       | 0    |                                                   |

| DDR_A_4                  | 27       | 0    |                                                   |

| DDR_A_5                  | 26       | 0    |                                                   |

| DDR_A_6                  | 25       | О    |                                                   |

| DDR_A_7                  | 24       | 0    |                                                   |

| DDR_A_8                  | 22       | 0    |                                                   |

| DDR_A_9                  | 21       | 0    |                                                   |

| DDR_A_10                 | 35       | 0    | FIFOTDONIO                                        |

| DDR_A_11                 | 20       | 0    | ELECTRONIC                                        |

| DDR_A_12                 | 19       | O    |                                                   |

Table 1-2. Signal-to-Pin Relationships and Descriptions (continued)

| Symbol               | LQFP-128<br>Pin | Туре | Description                                                                              |

|----------------------|-----------------|------|------------------------------------------------------------------------------------------|

| DDR_DATA_0           | 120             | I/O  | DDR data bus                                                                             |

| DDR_DATA_1           | 121             | I/O  |                                                                                          |

| DDR_DATA_2           | 122             | I/O  |                                                                                          |

| DDR_DATA_3           | 123             | I/O  |                                                                                          |

| DDR_DATA_4           | 124             | I/O  |                                                                                          |

| DDR_DATA_5           | 125             | I/O  |                                                                                          |

| DDR_DATA_6           | 126             | I/O  |                                                                                          |

| DDR_DATA_7           | 127             | I/O  |                                                                                          |

| DDR_DATA_8           | 11              | I/O  |                                                                                          |

| DDR_DATA_9           | 10              | I/O  |                                                                                          |

| DDR_DATA_10          | 9               | I/O  |                                                                                          |

| DDR_DATA_11          | 8               | I/O  |                                                                                          |

| DDR_DATA_12          | 7               | I/O  |                                                                                          |

| DDR_DATA_13          | 6               | I/O  |                                                                                          |

| DDR_DATA_14          | 5               | I/O  |                                                                                          |

| DDR_DATA_15          | 4               | I/O  |                                                                                          |

| LED                  |                 |      |                                                                                          |

| LED_0 <sup>[1]</sup> | 90              | OD   | If ETH_SWITCH_LED0_EN is set, it becomes open drain and provides drive strength of 10 mA |

| LED_1 <sup>[1]</sup> | 91              | OD   | If ETH_SWITCH_LED1_EN is set, it becomes open drain and provides drive strength of 10 mA |

| LED_2 <sup>[1]</sup> | 92              | OD   | If ETH_SWITCH_LED2_EN is set, it becomes open drain and provides drive strength of 10 mA |

| LED_3 <sup>[1]</sup> | 109             | OD   | If ETH_SWITCH_LED3_EN is set, it becomes open drain and provides drive strength of 10 mA |

| LED_4 <sup>[1]</sup> | 110             | OD   | If ETH_SWITCH_LED4_EN is set, it becomes open drain and provides drive strength of 10 mA |

ELECTRONIC

*Table 1-2.* Signal-to-Pin Relationships and Descriptions (continued)

| Symbol             | LQFP-128<br>Pin | Туре  | Description                           |

|--------------------|-----------------|-------|---------------------------------------|

| JTAG               |                 |       | · ·                                   |

| EJTAG_SEL          | 79              | I     | 0 JTAG                                |

|                    |                 |       | 1 EJTAG (enhanced JTAG)               |

| TCK <sup>[1]</sup> | 85              | I     | JTAG/EJTAG clock                      |

| TDI <sup>[1]</sup> | 81              | I     | JTAG/EJTAG data input                 |

| TDO <sup>[1]</sup> | 82              | 0     | JTAG/EJTAG data output                |

| TMS <sup>[1]</sup> | 84              | I     | JTAG/EJTAG mode select                |

| Ethernet           |                 |       |                                       |

| RBIAS              | 66              | OA    | Connect to 2.37 KΩ resistor to ground |

| RXN0               | 62              | IA/OA | Port 0                                |

| RXP0               | 61              | IA/OA |                                       |

| TXN0               | 64              | IA/OA |                                       |

| TXP0               | 63              | IA/OA |                                       |

| RXN1               | 59              | IA/OA | Port 1                                |

| RXP1               | 58              | IA/OA |                                       |

| TXN1               | 57              | IA/OA |                                       |

| TXP1               | 56              | IA/OA |                                       |

| RXN2               | 52              | IA/OA | Port 2                                |

| RXP2               | 51              | IA/OA |                                       |

| TXN2               | 54              | IA/OA |                                       |

| TXP2               | 53              | IA/OA |                                       |

| RXN3               | 49              | IA/OA | Port 3                                |

| RXP3               | 48              | IA/OA |                                       |

| TXN3               | 47              | IA/OA |                                       |

| TXP3               | 46              | IA/OA |                                       |

| RXN4               | 42              | IA/OA | Port 4                                |

| RXP4               | 41              | IA/OA | ELECTRONIC                            |

| TXN4               | 44              | IA/OA |                                       |

| TXP4               | 43              | IA/OA |                                       |

Table 1-2. Signal-to-Pin Relationships and Descriptions (continued)

| Symbol                    | LQFP-128<br>Pin | Туре | Description                                                     |  |

|---------------------------|-----------------|------|-----------------------------------------------------------------|--|

| GPIO GPIO                 | 1               | -36- |                                                                 |  |

| GPIO_0 <sup>[1]</sup>     | 107             | I/O  | General purpose input/output with drive strength of 2 mA.       |  |

| GPIO_1 <sup>[1]</sup>     | 108             | I/O  |                                                                 |  |

| GPIO_2 <sup>[1]</sup>     | 80              | I/O  |                                                                 |  |

| GPIO_3 <sup>[1]</sup>     | 76              | I/O  |                                                                 |  |

| GPIO_4 <sup>[1]</sup>     | 77              | I/O  |                                                                 |  |

| GPIO_5 <sup>[1]</sup>     | 78              | I/O  |                                                                 |  |

| <br>GPIO_6 <sup>[1]</sup> | 81              | I/O  | GPIO pin multiplexed as TDI by default                          |  |

| GPIO_7 <sup>[1]</sup>     | 82              | I/O  | GPIO pin multiplexed as TDO by default                          |  |

| GPIO_8 <sup>[1]</sup>     | 84              | I/O  | GPIO pin multiplexed as TMS by default                          |  |

| GPIO_9 <sup>[1]</sup>     | 86              | I/O  | General purpose input/output with drive strength of 2 mA.       |  |

| GPIO_10 <sup>[1]</sup>    | 87              | I/O  |                                                                 |  |

| GPIO_11 <sup>[1]</sup>    | 88              | I/O  |                                                                 |  |

| GPIO_12 <sup>[1]</sup>    | 89              | I/O  |                                                                 |  |

| GPO_13 <sup>[1]</sup>     | 90              | О    | These pins are intended for driving Ethernet LEDs and cannot be |  |

| GPO_14 <sup>[1]</sup>     | 91              | 0    | used as inputs. See the pin descriptions for "LED" on page 10.  |  |

| GPO_15 <sup>[1]</sup>     | 92              | 0    |                                                                 |  |

| GPO_16 <sup>[1]</sup>     | 109             | 0    |                                                                 |  |

| GPO_17 <sup>[1]</sup>     | 110             | 0    |                                                                 |  |

| GPIO_18 <sup>[1]</sup>    | 85              | I/O  | GPIO pin multiplexed as TCK by default                          |  |

| GPIO_19 <sup>[1]</sup>    | 79              | I/O  | GPIO pin multiplexed as EJTAG_SEL by default                    |  |

| I <sup>2</sup> S/SPDIF    |                 | 7    |                                                                 |  |

| I2S_CK <sup>[1]</sup>     | 81, 108,        | 0    | Stereo clock                                                    |  |

| I2S_MCK <sup>[1]</sup>    | 109             | 0    | Master clock LECTRONC                                           |  |

| I2S_MICIN <sup>[1]</sup>  | 89              | I    | Data input                                                      |  |

| I2S_SD <sup>[1]</sup>     | 84, 89, 91      | I/O  | Serial data input/output                                        |  |

| I2S_WS <sup>[1]</sup>     | 82, 92, 107     | 0    | Word select for stereo                                          |  |

| 120_770                   |                 |      | 0 Right                                                         |  |

|                           |                 |      | 1 Left                                                          |  |

| SPDIF_OUT <sup>[1]</sup>  | 85, 90          | О    | Speaker output                                                  |  |

<sup>[1]</sup>This pin is multiplexed. See Table 1-1.

| Symbol            | Pin                                 | Descr              | iption                                                                                                                                                                |  |

|-------------------|-------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Regulator Contro  | ol                                  |                    |                                                                                                                                                                       |  |

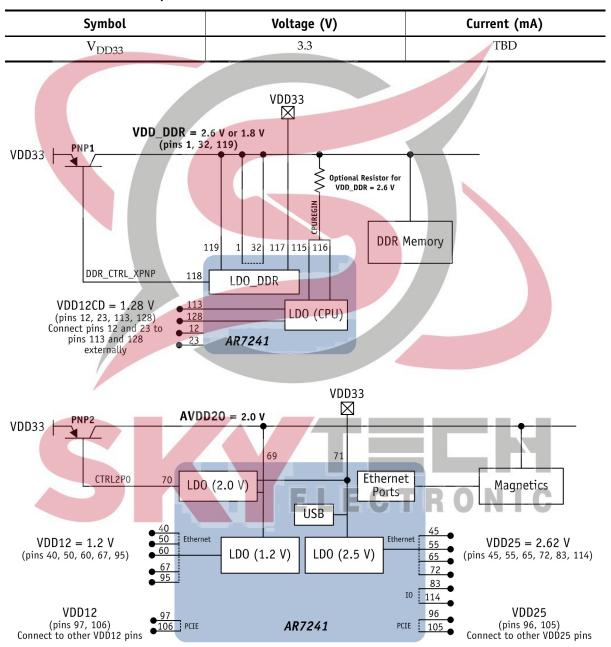

| CPUREGIN          | 115, 116                            | I                  | CPU regulator control inputs. Minimum voltage is 1.8 V. A 1 $\Omega$ resistor may be used in series between these pins and VDD_DDR pins in DDR1 mode (LDO_DDR_SEL=1). |  |

| CTRL_DDR<br>_XPNP | 118                                 | OA                 | External PNP Control. Connect to the base of an external PNP: collector to VDD_DDR and emitter to VDD33.                                                              |  |

| CTRL2P0           | 70                                  | OA                 | External PNP control. Connect to the base of an external PNP: collector to AVDD20 and emitter to VDD33.                                                               |  |

| LDO_DDR_SEL       | 112                                 | I                  | Selects the regulated DDR voltage, see VDD_DDR description                                                                                                            |  |

|                   |                                     |                    | 0 DDR2 voltage, 1.8 V                                                                                                                                                 |  |

|                   |                                     |                    | 1 DDR1 voltage, 2.6 V                                                                                                                                                 |  |

| Power             |                                     |                    |                                                                                                                                                                       |  |

| AVDD20            | 69                                  | Regula<br>collect  | ated 2.0 V from the AR7241; connect to the external PNP cor.                                                                                                          |  |

| VDD_DDR           | 1, 32, 119                          |                    | ated 2.6 V or 1.8 V output from the AR7241, for DDR1 or respectively. Connect to the external PNP collector.                                                          |  |

| VDD12             | 40, 50, 60, 67, 95, 97, 106         | Regula             | ated 1.2 V output from the AR7241                                                                                                                                     |  |

| VDD12CD           | 12, 23, 113, 128                    |                    | ated 1.28 V output from the AR7241; core voltage of CPU/<br>blocks, connect pins 12 and 23 to pins 113 and 128                                                        |  |

| VDD25             | 45, 55, 65, 72, 83, 96, 105,<br>114 | Regula             | ated 2.62 V output from the AR7241; I/O voltage                                                                                                                       |  |

| VDD33             | 71, 117                             | 3.3 V <sub>I</sub> | power supply                                                                                                                                                          |  |

| <b>Ground Pad</b> |                                     |                    |                                                                                                                                                                       |  |

| Exposed Ground    | Pad                                 | Tied to            | o GND (see "Package Dimensions" on page 36)                                                                                                                           |  |

| No Connection     |                                     |                    |                                                                                                                                                                       |  |

| NC                | 68                                  | No co              | nnection                                                                                                                                                              |  |

| S                 | SKATECH                             |                    |                                                                                                                                                                       |  |

|                   |                                     |                    | ELECTRONIC                                                                                                                                                            |  |

## 2. System Architecture

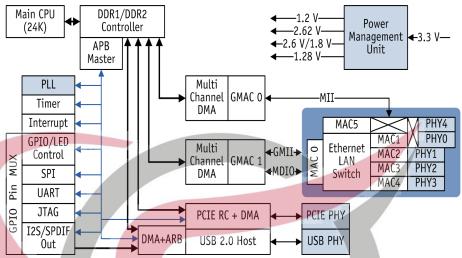

Figure 2-1 illustrates the AR7241 system architecture.

Figure 2-1. AR7241 Functional Block Diagram

Table 2-1 summarizes the functional blocks that comprise the AR7241.

Table 2-1. Functional Block Descriptions

| Block                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                         | This MIPS 24 K processor can run up to 400 MHz. It includes a 64 K 4-way set associative instruction cache, 32 K 4-way set associative data cache, single cycle multiply-accumulate, and MIPS32 and MIPS16 instruction sets. Non-blocking cache reads are also supported.  See "MIPS Processor" on page 16.                                                                                                                                                                                  |

| DDR<br>Memory<br>Controller |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                             | See "DDR Memory Controller" on page 17.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Ethernet<br>Switch/<br>GMAC | Four LAN ports and one WAN port with integrated PHY. LED indication for each port is supported. The four LAN ports connect to the CPU through the GE1 GMII interface, and four Tx queue priorities are supported in each LAN port. The WAN port connects to the CPU using the GE0 MII interface. The MII interface can support up to four priority queues, with either simple priority or a weighted round robin arbitration mechanism. Switch functions such as QoS and VLAN are supported. |

| Bus<br>Bridge               | High speed peripheral bus; the APB connects peripherals such as GPIO, UART, and SPI for Flash to the bus bridge. The AHB connects high-performance peripheral interfaces such as the GB Ethernet and USB interfaces to the bus bridge.  See "AHB Master Bus" on page 17 and "APB Bridge" on page 17.                                                                                                                                                                                         |

| GPIO                        | 20 multiplexed GPIO pins: 5 of which are output-only intended for driving LEDs, the others can be used for general purpose controls, SPI, I <sup>2</sup> S, SPDIF, and UART. See Table 1-1 on page 7 for GPIO multiplexing.                                                                                                                                                                                                                                                                  |

Table 2-1. Functional Block Descriptions (continued)

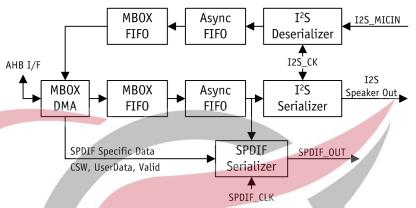

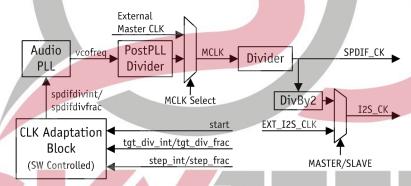

| I <sup>2</sup> S/ | AR7241 audio support consists of:                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPDIF             | ■ I <sup>2</sup> S/SPDIF out audio interface that support up to 48 KHz sampling clock and a serial clock of more than 512 * sampling frequency. It also supports seamless switching of the audio out stream from I2S to SPDIF. I2S MIC is also supported.                                                                                                                                                                                                                         |

|                   | ■ A dedicated audio PLL to generate serial clock for various sampling frequencies.                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | See "Audio Interface" on page 25.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PCIE              | The root complex single lane interface can support up to 2.56 Gbps and supports both the message-based and MSI interrupt mechanism.                                                                                                                                                                                                                                                                                                                                               |

| PLL               | The PLL block consists of six PLLs used to generate:  ■ A clock for CPU/DDR, tunable from 300 MHz to 450 MHz  ■ PLL for 48 MHz reference clock for the USB core and to generate a 25 MHz reference clock for the Ethernet Switch  ■ PCIE 100 MHz clocks with dither support  ■ PCIE PHY PLL generates 250 MHz and 2.5 GHz clock for the PCIE interface  ■ Ethernet 125 MHz clock generated from a 25 MHz clock  ■ PLL to generate the master clock for I <sup>2</sup> S/SPDIF out |

| SPI               | SPI interface that can be used for serial Flash.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| UART              | 16650 equivalent UART for debug/console                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| USB               | Universal Serial Bus 2.0 host interface support.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## 2.1 MIPS Processor

The AR7241 integrates an embedded MIPS 24Kc processor. For complete information on the 24Kc processor, visit:

http://www.mips.com/products/cores/32bit\_cores/MIPS32\_24K\_Family.php#

Under Processor Cores-24K Family, refer to:

- MIPS32 24Kc Processor Core Datasheet v3.04

- MIPS32 24Kc Processor Core Family Software User's Manual v3.05

Under EJTAG, refer to:

■ EJTAG Specification v2.60

## 2.2 Configuration

Table 2-2 summarizes the configuration settings used by the AR7241. Upon reset, the CPU puts out an address of 0xBFC00000 which is mapped to the flash address space.

The AR7241 processor supports a clock frequency of up to 400 MHz.

## **Table 2-2.** Core Processor Configuration Settings

| Setting          | Description                                                                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cache Size       | The AR7241 implements 64 KB 4-way set associative instruction cache and 32 KB four-way set associative data cache. It supports single cycle multiply-accumulate, MIPS32 and MIPS16 instruction sets and non-blocking cached reads. |

| Endian           | The AR7241 implements big Endian addressing.                                                                                                                                                                                       |

| Block Addressing | The AR7241 implements sequential ordering.                                                                                                                                                                                         |

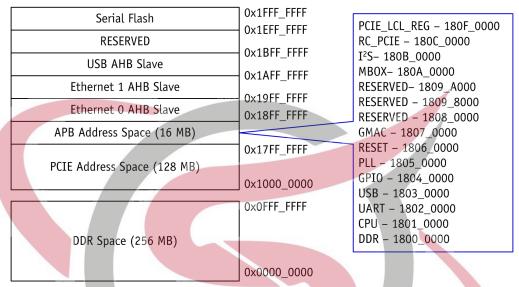

#### 2.3 AR7241 Address MAP

The address space for the AR7241 is divided into two 256 MBytes (MB) regions. The lower region maps to the DDR memory. The upper region maps to the AHB bus bridge. The

512 MBytes decoded region is repeated through the 4 GBytes of the processor's address space. Figure 2-2 shows the address space allocation.

Figure 2-2. Address Space Allocation

### 2.4 AHB Master Bus

The 256 MByte region of address space for the AHB devices is divided into two major windows, 128 MByte for the PCIE and the remainder for the internal DDR AHB master interfaces such as APB, GE0, GE1, and serial flash.

#### 2.5 APB Bridge

One 16 MByte window of the AHB address space is devoted to an APB device mapper. The APB space contains the register address spaces of most of the interfaces, including PCIE, serial flash, GPIO, and UART. This space also provides access to the watchdog timer and four general purpose timers.

## 2.6 DDR Memory Controller

The AR7241 supports a 16-bit DDR1/DDR2 memory interface of up to 64 MBytes of memory in a single device. It supports one dedicated point-to-point interface for the CPU and similarly dedicated point-to-point interfaces for the CPU, USB, Ethernet and PCIE master devices. Write transactions are buffered at each interface. It implements separate arbitration for each bank thus allowing efficient pipelined RAS/CAS/precharge scheduling.

The DDR block has five AHB-slave interfaces for: GE0, GE1, USB, PCIE, and CPU. External DDR is powered by the AR7241 using an external power transistor. Depending on the LDO\_DDR\_SEL input, the AR7241 internal regulator generates VDD\_DDR output voltage to power the external DDR memory. Table 2-3 shows the LDO\_DDR\_SEL configurations.

Table 2-3. LDO\_DDR\_SEL Voltage Configuration

| LDO-DDR_SEL Input | DDR Voltage | Device Type |

|-------------------|-------------|-------------|

| 0                 | 1.8 V       | DDR2        |

| FCTD              | 2.6 V       | DDR1        |

|                   |             |             |

See Figure 4-1, "Output Voltages Regulated by the AR7241," on page 33.

Table 2-4 shows the DDR configurations.

Table 2-4. DDR Configurations

| Device Type/Total Cap. | <b>Device Count</b> | Device Type |

|------------------------|---------------------|-------------|

| 128 MB (8 M x 16)      | 1                   | DDR1        |

| 256 MB (16 M x 16)     | 1                   | DDR1        |

| 256 MB (16 M x 16)     | 1                   | DDR2        |

| 512 MB (32 M x 16)     | 1                   | DDR2        |

Table 2-5 shows the correspondence of the internal CPU address, the DDR interface address, and the physical memory address.

Table 2-5. Address Mapping

| CPU Address Bit | AR7241<br>DDR Interface Address | Corresponding 16-bit DDR<br>Memory Address <sup>[1]</sup> |

|-----------------|---------------------------------|-----------------------------------------------------------|

| 0               | DDR_A_0, Unused (x16 DRAM)      |                                                           |

| 1               | DDR_A_1                         | CAS0                                                      |

| 2               | DDR_A_2                         | CAS1                                                      |

| 3               | DDR_A_3                         | CAS2                                                      |

| 4               | DDR_A_4                         | CAS3                                                      |

| 5               | DDR_A_5                         | CAS4                                                      |

| 6               | DDR_A_6                         | CAS5                                                      |

| 7               | DDR_A_7                         | CAS6                                                      |

| 8               | DDR_A_8                         | CAS7                                                      |

| 9               | DDR_A_9                         | CAS8                                                      |

| 10              | DDR_A_0                         | RAS0                                                      |

| 11              | DDR_BA_0                        | BA0                                                       |

| 12              | DDR_BA_1                        | BA1                                                       |

| 13              | DDR_A_1                         | RAS1                                                      |

| 14              | DDR_A_2                         | RAS2                                                      |

| 15              | DDR_A_3                         | RAS3                                                      |

| 16              | DDR_A_4                         | RAS4                                                      |

| 17              | DDR_A_5                         | RAS5                                                      |

| 18              | DDR_A_6                         | RAS6                                                      |

| 19              | DDR_A_7                         | RAS7                                                      |

| 20              | DDR_A_8                         | RAS8                                                      |

| 21              | DDR_A_9                         | RAS9                                                      |

| 22              | DDR_A_10                        | RAS10                                                     |

| 23              | DDR_A_11                        | RAS11                                                     |

| 24              | DDR_A_12                        | RAS12                                                     |

| 25              | DDR_A_11                        | CAS9                                                      |

| 26              | DDR_A_12                        | CAS11                                                     |

[1]CAS10 is a precharge bit, typically 0.

## 2.7 Serial Flash (SPI)

The single SPI chip select is dedicated to an external flash to boot the chip. Two configurable chip selects are available to bitbang using GPIOs that configure external components. As an AHB slave, the SPI controller only supports word transactions. Because serial flash supports cached reads (but not cached writes) functionality, the CPU must perform uncached write, but a read can be accelerated by performing cached reads. By default, the REMAP\_DISABLE bit is zero

## ELECTRONIC

which only 4 MBytes are accessible. By setting this bit to 1, up to 16 MBytes of flash space can be accessed.

#### 2.8 *UART*

The AR7241 contains a single 16550 equivalent UART port for debug/console. The UART pins are multiplexed with GPIO pins, therefore the "GPIO Function (GPIO\_FUNCTION\_1)"

register bits control which GIPIO pins are used for UART functions.

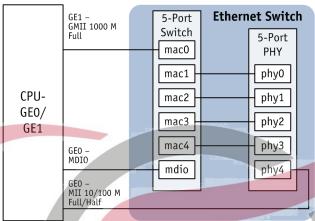

#### 2.9 GEO and GE1

The AR7241 integrates two Gigabit Ethernet ports that are connected to the Ethernet Switch. The GE0 and GE1 support 2K transmit FIFO and 2K receive FIFO. The WAN port is a MII interface that connects directly to a PHY inside the Ethernet Switch. Another port connects to the Ethernet Switch using a GMII interface. Through the Ethernet Switch this port connects to the four LAN ports. See Figure 2-3.

The AR7241's WAN Ethernet PHY (PHY0) can connect directly to the switch as another port, or can be directly to the CPU through an MII interface.

The PHY interfaces (PHY0, PHY1, PHY2, PHY3 and PHY4) can connect to the switch in bridge mode. In this case GE0 must be under reset. All five LAN ports are switched together and connect to the CPU through the GMII interface (MAC0), which is controlled by the ETH\_CFG register bit SW\_ONLY\_MODE. If GEO connects separately to PHY, then MAC5 should be under reset.

The GMII and MII MAC interface to the Ethernet Switch support four Tx queues, each with its own descriptor chain. A priority of DMA\_TX\_Q0 is higher than DMA\_TX\_Q1 and so on. The DMA configuration registers are separate for each queue. Two arbitration mechanisms are supported: one is a simple priority and the other is a weighted round robin arbitration.

Similarly for rest of the queues. In case of Round robin arbitration on a long term the number of packets sent per queue is guaranteed to be in the ratio of the weights programmed. Weight of ZERO is prohibited. It should be noted that the weights are on a packet basis and not on the number of bytes transmitted on that queue. Moreover, a 19-bit free running counter (running on AHB\_CLK) value is updated on the descriptor field as shown below on both the transmit and receive descriptor. This update is done as part of the descriptor update that the MAC DMA core already does upon completion of transmit or receive. Software can track the latency on per packet basis using these descriptor Timestamp and the free timer register.

## 2.10 MDC/MDIO Interface

The MDC/MDIO interface, which is internal to the AR7241, allows users to access the internal registers of the switch. Table 2-6 shows the format required to access the MII registers in the embedded PHY. The PHY-address is from 0x00 to 0x04. The OP code 10 indicates the read command and 01 indicates the write command.

Table 2-6. MDC/MDIO Interface Format

| start | Ор | 2′b0 | Phy-addr | reg_addr | TA    | Data   |

|-------|----|------|----------|----------|-------|--------|

|       | •  |      | [2.0]    | [4:0]    | [1:0] | [15:0] |

The internal switch registers are 32 bits wide, but MDIO access is only 16 bits wide, so two access cycles are required to access all 32 bits of the internal registers. Address spacing is more than the MDIO-supported 10 bits, thus upper address bits must be written to the internal registers, similar to the page mode access method. For example, register address bits [18:9] are treated as a page address and written out first as High\_addr [9:0] (see Table 2-7). Then the register would be accessed via Table 2-6, where Low\_addr [7:1] is the register address bit [8:2] and Low\_addr [0] is 0 for Data [15:0] or Low\_addr [0] is 1 for Data [31:16].

Table 2-7. Initial Register Address Bits

| start | Op | 2'b11 | 8′b0 | 6′b0 | High_addr<br>[9:0] |

|-------|----|-------|------|------|--------------------|

|       |    |       |      |      |                    |

## 2.11 Ethernet Switch Controller

Figure 2-3 shows the Ethernet Switch block diagram.

Notes:

- 1. macO connects to the CPU port and only supports 1000M full duplex mode.

- 2. phy4 connects to the CPU directly and supports 10/100M full and half duplex.

- 3. The MDIO interface connects the Ethernet switch to the configuration register.

Figure 2-3. Ethernet Switch Block Diagram

The Ethernet Switch controller performs the majority of the switch functions of the AR7241. The controller contains five 10/100 Mbps Fast Ethernet ports, each containing four levels of Quality of Service, 802.1Q VLANs, port based VLANs and RMON statistic counters. The AR7241 integrates five 10/100 two speed Ethernet transceivers (PHYs) and one single port 10/100/1000 media access controllers (MAC) as well as a wire-speed, non-blocking shared memory switch fabric.

The included 1 KB entry address lookup table uses two entries per bucket to avoid hash collisions and maintain packet-forwarding performance. The address entry table provides read/write access from the serial and CPU interfaces where each entry can be configured as a static entry. 1024 MAC addresses are supported with automatic learning, aging and static address support. The Ethernet Switch also supports basic switch features including port mirroring, broadcast storm support, flow control in full-duplex, and back pressure in half duplex, 802.3 auto-negotiation, port locking, MIB counters, ingress and egress rate limitation, and automatic speed and duplex communication between PHYs and MACs.

Table 2-8 summarizes the AR7241 Ethernet Switch functions.

Table 2-8. Ethernet Switch

| Block                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Media Access<br>Controllers<br>(MAC) | The AR7241 integrates six independent fast Ethernet MACs that perform all functions in the IEEE 802.3 and IEEE 802.3u specifications, including frame formatting, frame stripping, CRC checking, CSMA/CD, collision handling, and back-pressure flow control, etc. Each MAC supports 10 Mbps or 100 Mbps operation in either full-duplex or half-duplex mode.                                                                                                           |

| Full-Duplex<br>Flow Control          | The AR7241 device supports IEEE 802.3x full-duplex flow control, force-mode full-duplex flow control, and half-duplex back pressure. If the link partner supports auto-negotiation, the 802.3x full-duplex flow control auto-negotiates between the remote node and the AR7241. If full-duplex flow control is enabled, when free buffer space is almost empty, the AR7241 sends out an IEEE 802.3x compliant PAUSE to stop the remote device from sending more frames. |

| Half-Duplex<br>Flow Control          | Half-duplex flow control regulates the remote station to avoid dropping packets during network congestion. A back pressure function is supported for half-duplex operations. When free buffer space is almost empty, the AR7241 device transmits a jam pattern on the port and forces a collision. If the half-duplex flow control mode is not set, the incoming packet is dropped if no buffer space is available.                                                     |

| Inter-Packet<br>Gap (IPG)            | The IPG is the idle time between any to successive packets from the same port. The typical IPG is 9.6 µs for 10 Mbps Ethernet and 960 µs for 100 Mbps Fast Ethernet.                                                                                                                                                                                                                                                                                                    |

| Port Locking                         | The AR7241 supports port locking. If one port is set for port locking, only received frames with the unicast source address found in the ARL table and do not have a member violation, can be sent out. Other blocked frames are dropped or redirected to the CPU port by the control register, LOCK_DROP_EN.                                                                                                                                                           |

| Frame<br>Forwarding<br>Prevention    | The AR7240 can be configured to prevent the forwarding of unicast or multicast frames that contain an unknown destination address. This can be accomplished on a per-port basis, so that frames with unknown addresses only go out to the port where a server or router is connected. Broadcast frames forwarded to the CPU port can also be prevented.                                                                                                                 |

| Illegal Frames                       | The AR7240 discards all illegal frames such as CRC error, oversized packets (length greater than maximum length), and runt packets (length less than 64 bytes).                                                                                                                                                                                                                                                                                                         |

| VLANs                                | See "VLANs For LAN Ports" on page 22.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| QoS                                  | See "Quality of Service (QoS) For LAN Ports" on page 23.                                                                                                                                                                                                                                                                                                                                                                                                                |

#### 2.11.1 VLANs For LAN Ports

The switch supports 16 IEEE 802.1Q VLANs and port-based VLAN functionality for all frames, including management frames when 802.1Q is enabled on the ingress port. Untagged frames conform to the port-based VLAN even if the ingress port has 802.1Q mode enabled. See Table 2-9.

Table 2-9. Ethernet Switch VLAN

| VLAN                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port-Based           | Each ingress port contains a register restricting the output (or egress) ports it can send frames to. This port-based VLAN register has a field called PORT_VID_MEM that contains the port based setting. If bit [0] of PORT_VID_MEM is set to one, the port is allowed to send frames to Port 0, bit [2] for Port 2, and so on. At reset, each port's PORT_VID_MEM is set to a value of all 1s, except for each port's own bit, which clears to zero. Note that the CPU port is port 0. |

| IEEE 802.1Q<br>VLANs | The AR7241 supports a maximum of 16 entries in the VLAN table. The device supports 4096 VLAN ID range from 0 to 4095. The AR7241 only supports shared VLAN learning (SVL). This means that forwarding decisions are based on the frame's destination MAC address, which should be unique among all VLANs.                                                                                                                                                                                |

Tagging and untagging egress frames is supported using 802.1Q VLANs, or statically using Port Based VLANs. Frames may go out from the switch in three methods:

- Transmit Unmodified Untagged frames egress a port untagged while tagged frames leave tagged.

- Transmit Untagged Untagged frames leave a port unmodified while tagged frames leave untagged.

- Transmit Tagged Tagged frames leave a port unmodified while an IEEE tag is added to untagged frames before leaving.

When a tag is added to an untagged frame, the frame inserts directly after the frame's source address and includes four bytes.

- The first byte is always 0x81.

- The second byte is always 0x00.

- PRI bits indicate frame priority determined by the source port's priority setting.

- The CFI bit is always set to 0.

VID bits indicate the VID assigned to the frame as determined in the source port default VID.

A tagged frame leaving a port tagged may have its VID bits modified. If the ingressing frame's VID was 0x000, the ingress port's default VID is assigned to the frame instead.

Double Tagging is a method of isolating one IEEE 802.1Q VLAN from other IEEE 802.1Q VLANs in a hierarchical fashion that is compatible with IEEE 802.1Q ready switches, as long as those switches support a maximum frame size of 1526 bytes or more. In this way, an extra, or double, tag is placed in front of a frame's normal tag thereby increasing the frame's size by four bytes.

Ingress double tagging can be selected on a port-by-port basis. Typically, any port that has ingress double tagging enabled will also have egress double tagging enabled. Ingress double tagging enabled ports expect all ingress frames to contain an extra tag that must be removed from the frame before performing the port's ingress policy on the frame. In this mode, the ingress policy removes the first IEEE 802.3ac tag that appears after the source address in every frame. If the untagged frame is not modified, all data from the removed tags is ignored by the switch.

## 2.11.2 Quality of Service (QoS) For LAN Ports

The AR7241 recognizes the QoS information of ingress frames and map to different egress priority levels. The AR7241 determines the priority of the frames based on DA, TOS/TC, VLAN, and port. Each has an enable bit that can be applied. When more than one type of priority is selected, the order in which the frame priority should be applied can be determined. Priority enable bits and select order bits are set by port base at 0x110 for port 0, 0x210 for port 1, and so on.

| Priority<br>Determined         | Description                                                                                                                                       |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| DA                             | Set DA_PRI_EN bit [18] to 1 and add the address to the ARL table-set priority_over_en to 1. ARL priority bits [59:58] can be used as DA priority. |

| ToS/TC                         | Set IP_PRI_EN bit [16] to 1, and set the IP priority mapping register (0x60–0x6C).                                                                |

| VLAN                           | Set VLAN_PRI_EN (bit [17]) to 1, and set the TAG priority mapping register (0x70).                                                                |

| Port's<br>Default<br>Authority | Set PORT_PRI_EN to 1, and set port base register ING_PORT_PRIORITY (bits [19:28] in 0x108, 0x208, etc.).                                          |

When more than one priority enable bit is set to 1, bits [7:0] in 0x110, 0x210, etc. (DA\_PRI\_SEL, IP\_PRI\_SEL, VLAN\_PRI\_SEL, PORT\_PRI\_SEL) can determine the order in which the frame priority should be applied. If \*\_PRI\_SEL is set to 00, frame priority is determined by that first. Otherwise, priority is determined by which \*\_PRI\_SEL is set to 01, then 10, 11, etc.

On arrival, packets are directed into one of the four available priority queues based on:

- Priority bits in the header field

- The frame destination address (if in the ARL table with a defined priority with the priority bit is enabled)

- The frame VID (if in the VLAN table and the priority override is enabled)

- The 802.3 tag containing 802.1p priority information (if enabled on the port)

- The port's default priority as defined in the register

Each of the priority classification rules have enables so designers may use any combination; priority can be disabled or the order may be selected separately on a per-port basis. Congestion in the flow of packets for an extended period of time forces frames to drop without flow control. Higher priority flows receive a higher percentage of the open buffers, and this percentage is determined by the scheduling mode. Features such as back pressure and pause-frame control are implemented to supports zero packet loss during traffic congestion. The AR7241 ensures that all uncongested flows traverse the switch without degradation, regardless od congestion situations elsewhere in the switch.

QoS for the AR7241 may follow one of three priority schemes, either fixed, weighted fair, or a mixed mode scheme. In the fixed priority scheme, all egress packets leave the switch starting with the highest priority queue. Once that queue has been emptied, the next highest priority queue begins its packet dispersal until it has been emptied and so on. This method insures that all high priority packets will be sent out from the switch as soon as possible.

For the weighted fair scheme, packets are egressed from the chip in the order of 8, 4, 2, 1 packets for the four priorities queue of the AR7241. (eight packets egress from the highest priority queue, then four from the second highest queue, and so on). This method allows the highest priority to get its packets out first and the other remaining queues are not totally starved from egressing.

The mixed mode scheme mixes both the weighted fair and fixed schemes. The highest priority queue disperses its packets first until the queue has been emptied, and the remaining queues will follow the 4, 2, 1 weighted egress scheme as mentioned previously. This ensures that the highest priority queue will egress its packets as soon as possible, while the remaining queues equally disperse their packets without queue starvation.

## 2.12 Rate Limiting